Home »

Computer Science Organization

Computer Science Organization | Addressing Modes

In this article, we will learn about basic concept of Addressing modes in computer system organization. Classification of addressing modes is also prescribed in this article.

Submitted by Abhishek Kataria, on July 08, 2018

Addressing Modes

The term 'addressing mode' refers to the mechanism which will use to specify the operands. An operand can be specified as the part of the instruction, or the reference of the memory location which had given. An operand could also be an address of CPU register. Addressing modes can also be defined by the following criteria which are as follows:

- Addressing modes shows the way where exactly the required object is present.

- In this condition, object may be an instruction or data.

- The output of the addressing mode is Effective Address [EA], where EA is the actual address where exactly the object is present in the computer.

-

There is a different convention which is used to indicate the various addressing modes some of them follow here:

- #/I ------- Immediate addressing mode.

- Reg.Name -------Register addressing mode.

- [ ] ------------Direct addressing mode.

- @/ ( ) ----------Indirect addressing mode.

- Index Reg Name ------Indexed addressing mode.

- +/- -------------- Auto indexed addressing mode.

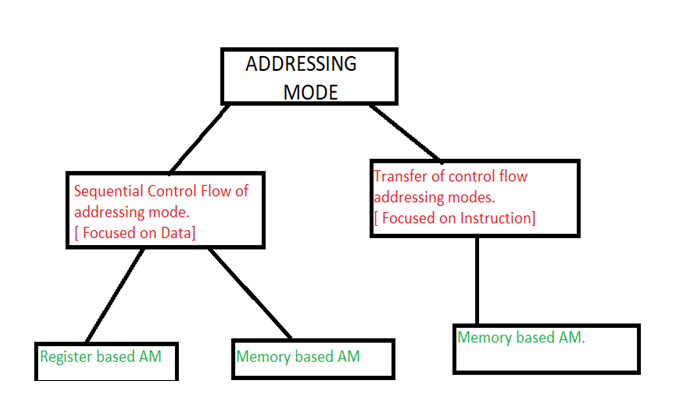

Classification of Addressing Modes

According to specify the operand in different ways, the addressing modes are classified in two ways that are:

- Sequential control flows addressing mode which is focused on data.

- Transfer of control flow addressing mode which is focused on instruction.

1) Sequential Control Flow Addressing Mode

These modes are concentrating on the location of data in a computer system. Basically, data is present in the computer in two possible places that are register and memory. Therefore these modes are further divided into two kinds:

- Register based addressing mode

- Memory based addressing mode

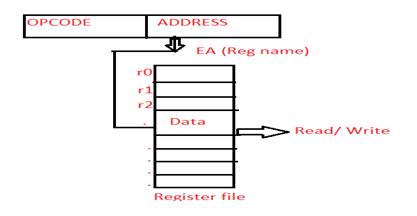

1. Register based addressing mode

These modes are used to access the data when it is in the register. Therefore effective address is always the register name. Under this category, only one addressing mode is employed i.e.

1.1 Register addressing mode

This mode is used to access the local variables. In this mode data is present in the register, therefore, reg.name is available in the address field of instruction.

2. Memory based addressing mode

These modes are used to access the data when it is in memory. Therefore EA is always the memory address. Under this category different addressing mode are employed they are:

2.1 Implied addressing mode

In this mode, data information is present in the opcode itself. Therefore EA is not required to access the data. In the CPU design, all the zero address instruction uses the implied addressing mode.

2.2 Immediate addressing mode

This mode is used to access the constants. In this mode, data is present in the address field of instruction so that EA is not required to access the data. Immediate AM may be used as a source but it never uses as a destination because destination always requires the storage capability but constantly does not have the storage.

2.3 Direct addressing mode

This mode is used to access the static variable. In this mode data is present in memory, that memory address is available in the address field of the instruction. In this mode, only one memory reference is required.

2.4 Indirect addressing mode

This mode is used to implement the pointers. In this mode, the address field of the instruction indicates the address of EA (loc of EA). In this mode, two references are required in which the first reference is to get the effective address and the second reference is to read/write the data.

2.5 Indexed addressing mode

This mode is used to implement the arrays. In which array elements are stored in the memory in the sequential cells. Array elements are referred to by the position called an index. For excess the array element there is a need of two parameters i.e. base address which is used to store the address of an array and another one is an index which is used to tell the position of the array element.

2.6 Auto indexed addressing mode

This mode is used to access the linear array element from the memory. To access the array element in a sequential order only one parameter is required i.e. base address. In this mode also the EA is obtained either by incrementing or by decrementing the base address with step size. In which step size depends upon amount of data to be accessed from the memory. It can be said it is fixed constant.

2) Transfer of control flow Addressing Mode

These modes are concentrating on the location of instruction on the computer. Two different AM are employed under this category to indicate the instruction address that is:

- PC Relative Addressing Mode

- Base Register Addressing Mode

These AM are associated with the help of the transfer of control instruction. So during the execution of these instructions, the EA is calculated. Then the calculated EA is placed into the PC so that in the next fetch cycle CPU reads the instruction from the target location.

1. PC–Relative Addressing Mode

This is a mode in which base address is common but offset address is different. So to calculate the offset address of the next instruction two parameters are required i.e. current location and another one is a relative value. Current location is pointed by the PC and the relative value is present in the address field of the instruction. In this mode when the target instruction is present in the same segment then during the execution, the control will be transfer within the segment called as Intra segment TOC.

2. Base Register Addressing Mode

In this operation the base address is different so the base register is used to hold the target segment base address. In this mode when the target instruction is present in different segment then during the program execution the control will be transfer between the segments called as inter segment TOC.