Home »

Computer Science Organization

Computer Science Organization | Instruction Format

In this article, we will learn about the concepts of instruction format in computer organization. On the basis of availability of ALU operands types of CPU organization are also prescribed in this article.

Submitted by Abhishek Kataria, on July 05, 2018

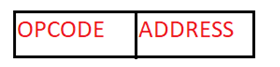

Instruction format

- Instruction format describes the internal structures (layout design) of the bits of an instruction, in terms of its constituent parts.

- An Instruction format must include an opcode, and address is dependent on an availability of particular operands.

- The format can be implicit or explicit which will indicate the addressing mode for each operand.

-

Designing of an Instruction format is very complex. As we know a computer uses a variety of instructional. There are many designing issues which affect the instructional design, some of them are given are below:

- Instruction length: It is a most basic issue of the format design. A longer will be the instruction it means more time is needed to fetch the instruction.

- Memory size: If larger memory range is to be addressed then more bits will be required in the address field.

- Memory organization: If the system supports the virtual memory then memory range which needs to be addressed by the instruction, is larger than the physical memory.

- Memory transfer length: Instruction length should be equal to the data bus length or it should be multiple of it.

- Instruction formats are classified into 5 types based on the type of the CPU organization. CPU organization is divided into three types based on the availability of the ALU operands, which are as follows here:

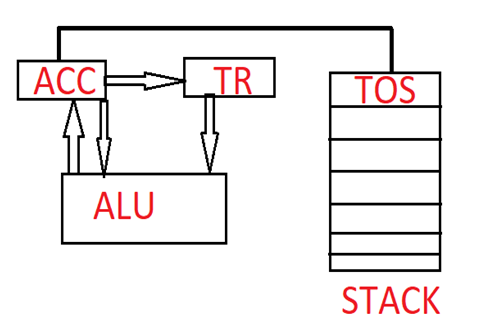

1) STACK CPU

In this organization, ALU operands are performed only on a stack data. This means that both of the ALU operations are always required in the stack. The same stack is also used as the destination. In the stack, we can perform insert and deletion operation at only one end which is called as the top of a stack. So in this format, there is no need of address because in this TOS becomes the default location.

In this organization, only the ALU operands are zero address operation whereas data transfer instructions are not a zero address instruction. The computable instruction format of STACK CPU is Zero Address Instruction Format.

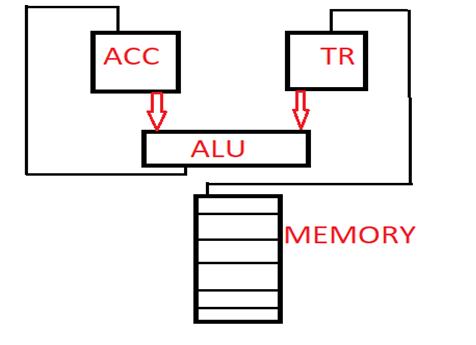

2) Accumulator CPU

In this organization, one of the ALU operands is always present in the accumulator. The same accumulator is also used as the destination. Another ALU operand is present either in the register or in memory. In processor design, only one accumulator is present so it becomes the default location.

The computable instruction format of Accumulator CPU is One Address Instruction Format.

3) General Register CPU

Based on the number of the registers possible in the processors, the architecture is divided into two types:

- Register-Memory references CPU

- Register-Register references CPU

i) Register-Memory Reference CPU

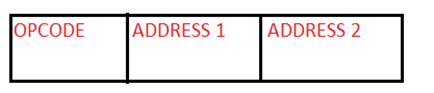

In this architecture, processors support less number of registers. Therefore register file size is small. In this organization, the first ALU operand is always required in the register. The same register can also be used as the destination. The second ALU operand is present either in a register or in memory. The computable instruction format of the register to memory reference CPU is Two Address Instruction Format.

ii) Register-Register Reference CPU

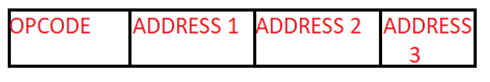

In this architecture, processors support number of registers, therefore, register file size is large. In this organization, ALU operands are performed only on a registers data that means both of the ALU operands are required in the register. Due to more number of register present in the CPU, the separate register is used to store the result. The computable instruction format of Register-Register Reference CPU is Three Address Instruction Format.

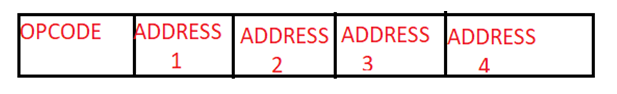

Four Address instruction format

This format contains the 4 different address fields with an opcode. Since PC is used as the mandatory register in the CPU design which is used to hold the next instruction address. So four instruction format is not in the use.