Home »

Computer Architecture

Cache Coherence Problem in Computer Architecture

In this article, we will discuss about the Cache Coherence Problem and its different protocols in Computer Architecture.

Submitted by Uma Dasgupta, on March 08, 2020

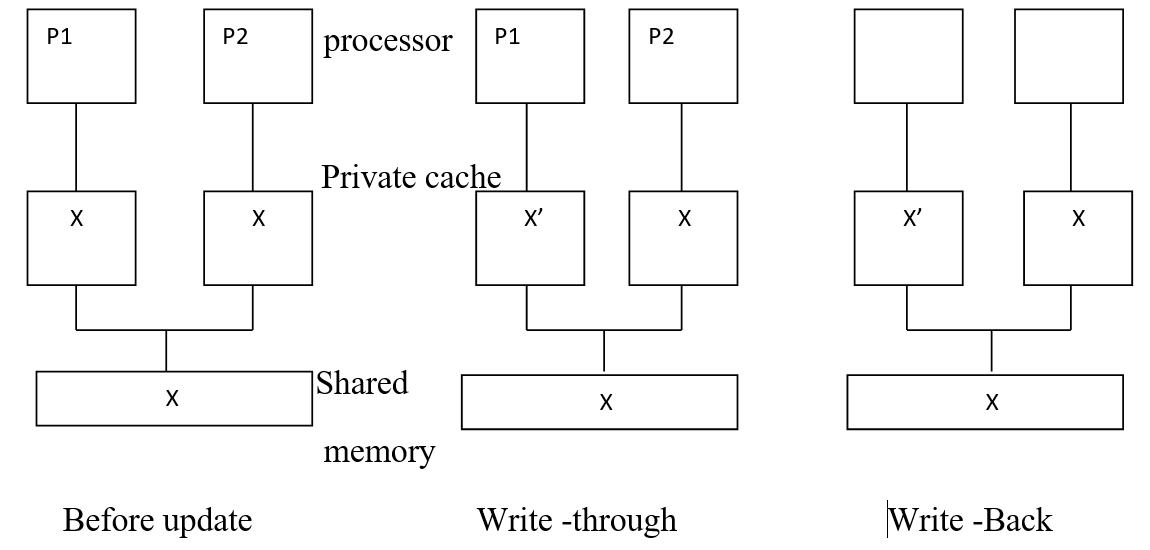

First of all, we will try to understand what cache coherence is? When multiple processors maintain a locally cached copy of a unique shared memory location. Any local modification of the location can result in a globally inconsistent view of memory. Cache inconsistencies are generally caused by data sharing, process migration or input, output. When there occurs an inconsistency in the sharing of co relatable data.

Suppose if a processor A writes some new data X' into the cache the same copy will be written immediately into the shared memory under a write-through policy. In this case, inconsistency occurs between the two copies because if some other write operation can take place before this update.

Snoopy-Based Protocol

In this using private cache associated with processor tied to a common bus, two approaches have been practiced for maintaining cache consistency:

- Write invalidate

- Write Broadcast/ Update policies

Cache coherence protocol

In this section, we will discuss one of the cache coherence protocols that are Directory-Based Protocol.

- Cache coherence protocol that does not use broadcast must store the locations of all cached copies of each block of shared data.

- The list of all cached locations whether centralized or distributed called cached hierarchy.

- Directory entry for each block of data contains no. of pointers to specify the location copies of the block.

- Each directory entry also contains a dirty bit to specify whether a particular cache has permission to write the associative block of data.

Steps

- Cache C3 detects that log containing location is valid but the processor does not have permission to write the block.

- Cache C3 issue is written request to the memory module containing location X, the memory modules issue invalidate request to caches C1 and C2.

- C1 and C2 receive the invalidate request set the appropriate bit to indicate that the block containing location X is invalid and sent acknowledged back to the memory.

- The memory module receives the acknowledgments sets the dirty bit, clears the pointer to catch C1 and C2 and sends writes permission to cache C3 receives the write permission, update the state in the cache and reactivate processor P3.

Conclusion:

In the above article, we have discussed the cache coherence and cache coherence protocol and its steps in brief. I hope till now after reading the above article you have a basic idea of cache coherence. For more queries shoot your questions in the comment section below.

Advertisement

Advertisement