Home »

Computer Architecture

Issues with Pipelining (Hazards) | Computer Architecture

In this tutorial, we are going to learn about the Issues with Pipelining (Hazards) in Computer Architecture.

Submitted by Uma Dasgupta, on March 04, 2020

Introduction:

When we hear about pipelining hazards the first thing that comes to our mind is what are pipeline hazards? So, pipeline hazards are simply any obstruction, condition or we can say any situation that is obstructing pipelines to work or act normally.

Generally, there are mainly three types of hazards:

- Structural Hazard

- Data Hazard

- Control Hazard

We will discuss all the hazards one by one, let's start with structural hazard

1) Structural Hazard

When we try to do multiple or two different things using the same hardware in the same clock cycle this prevents the pipeline to work properly this is known as structural hazard.

To avoid this situation processor can use stalling in the pipelining.

Stall of one cycle will shift the pipeline to the one clock cycle until hazard can fully be avoided or eliminated.

This situation or hazard will not occur if we had separate data cache and instruction cache.

2) Data Hazard

In data hazard, read and write operations of shared variables by different instructions in a pipeline may lead to different kind of data dependencies such as,

- Read after write hazard

- Write after reading hazard

- Write after write hazard

They arise when an instruction depends on the result of previous instruction is a way i.e exposed by overlapping of instructions in the pipelining.

To avoid data hazard we can do

- Internal forwarding

- Stalling

Internal forwarding- for avoiding the condition of reading after write hazard the latch which is placed right after ALU unit will be used as internal forwarding for transferring the output to the next instruction to the latch which is placed before the decoding unit.

Note: These are some other important terms related to data hazard:

- Data dependency

- Flow dependency - Register R1 is loaded by I1 and then used by I2. Hence, the result of one register after executing instruction may affect the operant of that register.

- Output dependency - when two instructions want to write the same time.

3) Control Hazard

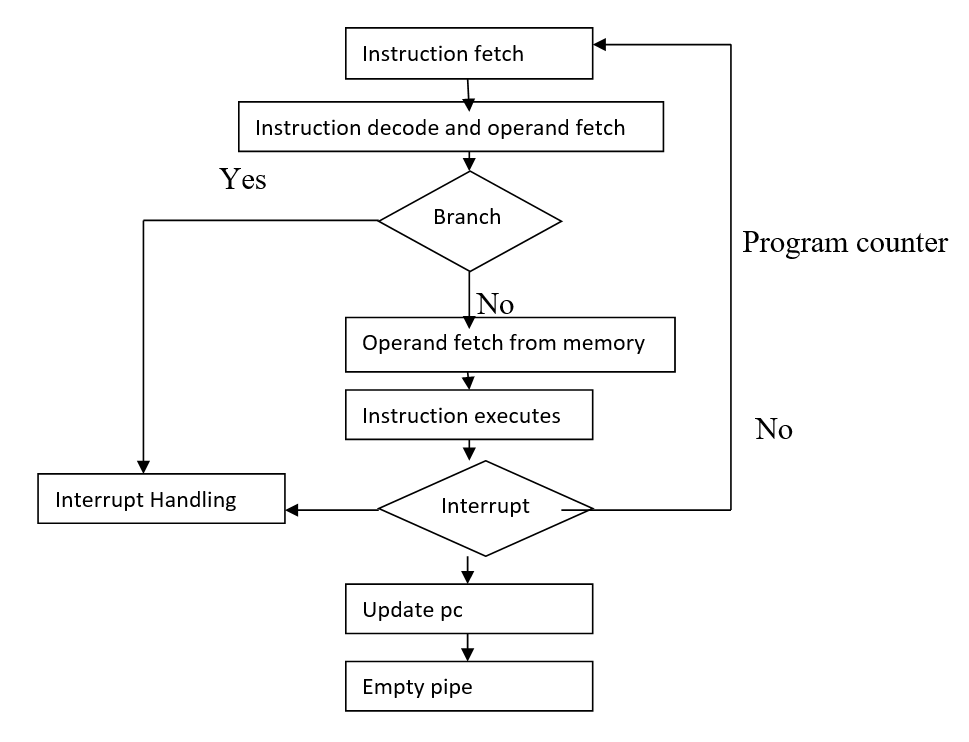

In simple words, we can say that control hazard occurs when we need to find the main root of any branch instruction, and cannot proceed further with another instruction till we get to root of that instruction.

Conclusion:

In this article, we have briefly discussed the different pipelining hazards. I hope that till now you have got a clear idea about the pipelining hazards. For any queries shoot your questions in the comment section.

Advertisement

Advertisement