Home »

Computer Science Organization

System Bus in Computers

In this article, we will learn basic concept of Bus in computer organization, categories of system bus and explanation on bus arbitration is also prescribed in this article.

By Abhishek Kataria Last updated : April 16, 2024

What is System Bus?

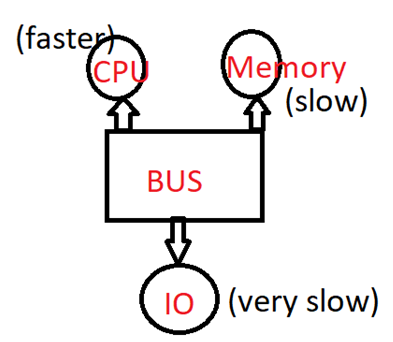

A bus is a communication channel which is used between the different nodes for providing the communication. The bus which is used to provide the communication between the CPU, Memory and IO components it is called as a system bus.

A set of connected lines is also called a bus. Basically, a bus is a bundle of wires that are grouped together to serve a single purpose in the microprocessor, in which there are three set of communication lines that are called buses.

System Bus Lines

The system bus is categorized on the basis of lines in three different formats for providing the effective communication:

1. Address lines

These lines are used to carry the address towards memory and IO components. Address lines are unidirectional. Based on the number of the address lines we can able to determine the capacity of the memory system.

Example: In 8085 microprocessors there are 16 address lines are present which means it contains 64 K memory locations.

2. Data lines

These lines are used to carry the binary sequence between the CPU, Memory and IO. So data lines are bidirectional. Based on the number of data lines we can determine word length of the processor and basis on the word length we can determine the performance of the processor.

3. Control lines

These lines are used to carry the control signal and timing signal. In which control signal indicates the type of operation and timing signal are used to synchronize the memory and IO operation with processor clock.

System Bus Arbitration

A bus has several units like (memory, IO and processor) which are connected to it. At any point of time any of these units may want to start a transaction. Arbitration is a process of deciding which unit will get access to the bus for driving the transaction. There are basically three bus arbitration mechanisms which are as follows here:

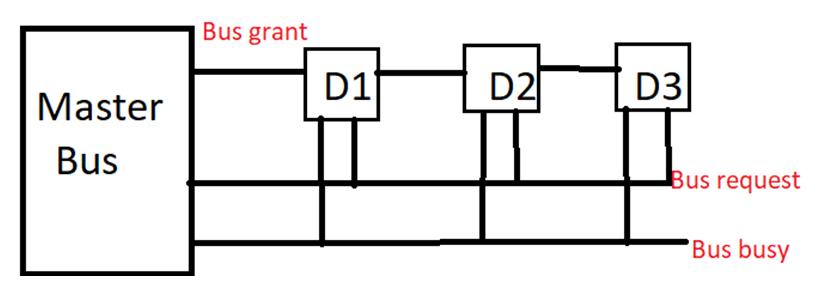

1. Daisy chaining

In this mechanism there are three bus lines which are Bus busy, Bus request and Bus grant which are arranged in daisy chaining fashion. This is simple to achieve and only contains three extra bus lines. This method has the poor fault tolerance and has the hardwired priority.

Steps to achieve daisy chaining mechanism

- Each devices checks, if bus is not busy then make bus request to the master.

- Then master see the bus request like high, and then it activates the bus grant.

- Then bus grant line travel from one device to another, in this time if a device gets a bus grant, mark the bus busy.

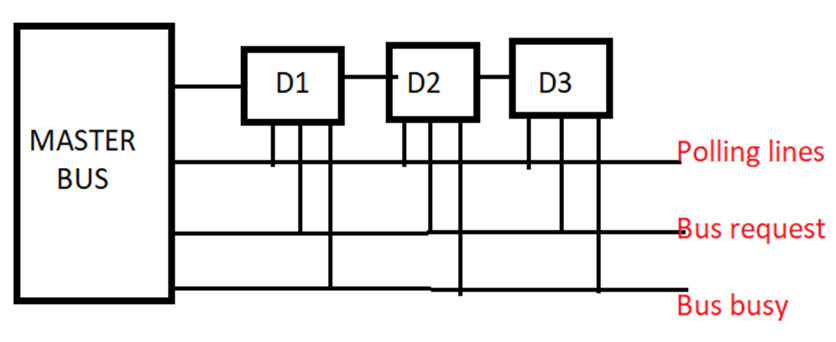

2. Polling

This is slightly a better mechanism. There is no such disadvantage of daisy chaining. It has the possibility of dynamic priority. In this mechanism we have the log n number of polling lines for n devices. Disadvantage of this mechanism is that, they contain extra poll lines and they have a polling delay.

Steps to achieve polling mechanism

- If bus is not busy, make bus request.

- Master polls by placing device on polling lines. In this master decides priority.

- If device gets access to the bus, mark bus busy.

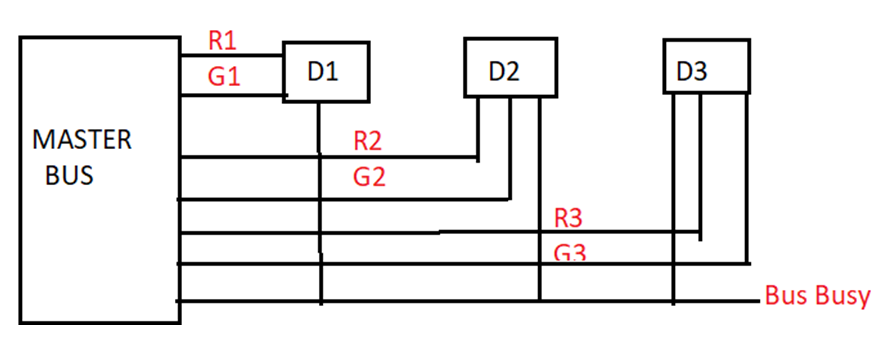

3. Independent request

This is the fastest mechanism in which also dynamic priority is possible. This is a mechanism in which we have request and grant lines for each of the devices with master. This mechanism has 2n lines for the n devices.

Steps to achieve independent request mechanism

- If bus is not busy, make bus request.

- Master decides who to grant access, and indicates through grant lines.

- If device gets bus grant, make bus busy.

Advertisement

Advertisement